Cadence Design Systems Sigrity 2019

v19.00.000 免费版大小:11.20G更新:2019-11-01

类别:行业软件系统:WinAll

分类

大小:11.20G更新:2019-11-01

类别:行业软件系统:WinAll

Cadence Sigrity 2019是一款专业的高速电路设计仿真软件,这款软件可以将PCB设计和分析扩展到封装和电路板之外。软件基于Sigrity专利技术,可以有效地提升各类高级物理设计的效率。新版本的Sigrity 2019还带来了全新的功能,优化了工作效率。

• 可以分析板上任意结构的电磁耦合特性,为器件/去耦电容的放置位置以及过孔的排布提供依据

• 可以提取IC封装电源网络与信号网络的阻抗(Z)参数及散射(S)参数,研究电源的谐振频率以及输入阻抗,或研究信号的插入损耗及反射系数,为精确分析电源和信号的性能提供依据; 为时域SSN仿真提供可靠的宽带网络参数模型

• 分析整板远场和近场的EMI/EMC性能,全三维显示复杂的近场辐射水平,为解决板级的EMI/EMC问题提供依据

• 分析板上任意位置的谐振特性,找出系统在实际工作时电源平面上的谐振及波动特性,为电源的覆铜方式及去耦电容的放置位置提供依据

• 支持叠层以及其他物理设计参数的假定(What-if)分析,快速评估设计参数对系统性能的影响

• 基于专利算法的精确直流求解引擎(PowerDC),可支持从直流(DC)到宽频段的精确模型提取

• 与三维(3D)IC封装设计和板级设计工具无缝集成

高速信号在传输的过程中由于layout走线的不良会导致反射串扰等信号完整性问题,这节我们仿真DDR信号特征阻抗和串扰参数,加深对layout的理解。

阻抗不匹配导致的反射失真

串扰

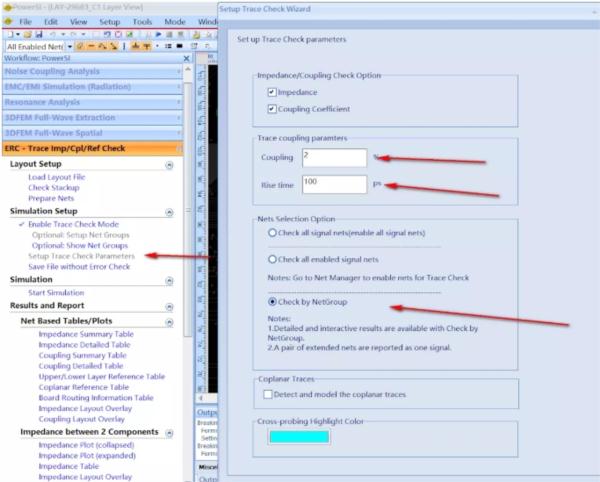

1. 打开PowerSI,load layout file。(我这图是已经仿真完了的)

2. 点击“Setup Net Groups”,选择TX 器件,这里勾选这个线路的CPU U12,点击下一步。

3. 选择RX端,这里勾选这个线路的DDR颗粒U11,点击下一步。

4. 确认电源网络/GND网络,直接点击下一步到分组界面,因为只是练习,我们把DDR的地址和数据等信号都分为一个组,真正项目需要分清楚;点击第一个,再shift点击最后一个,全分为一个组,命名为DDR,然后直接到finish。

5. 点击“Setup Trace Check Parameters”设置检查参数,默认是勾选阻抗和耦合,设置显示耦合2%以上,选择“根据group检查”,点击OK,开始仿真。

6. 仿真结果又表格形式和layout形式,我们偏向于看layout形式,需要具体点时可以再看表格。

7. impedance layout overlay会将CPU和DDR的走线以layout的形式显示出来,根据颜色区分。

阻抗柱状图也比较直观,每条线摘出来,这里不仅可以看到哪个地方阻抗偏高偏低,还可以看到走线长度。

8. coupling layout overlay通过颜色深浅将串扰强度表现出来,可以看出走线越近的地方串扰越大,一般低于5%信号质量不会受到太大影响。

提取码: 1fu9

fi Series Online Update富士通fi系列文档图像扫描仪在线升级行业软件MV1.2.2官方版

查看筑业建设工程计价软件行业软件MV3 2015版

查看拼多多助手多开版行业软件MV1.3.4增强版

查看小葫芦弹幕点歌插件行业软件Mv3.9.5官方版

查看2019PDF全能转换器(UniPDF)中文版行业软件Mv1.3

查看稻草人时间管理软件行业软件Mv1.0.0.0 绿色版

查看ACS门禁工程配置软件行业软件.68MV1.08官方版

查看威德几何尺电子量具行业软件.85M

查看ECbox星仔魔盒行业软件Mv4.0.0.12 官方版

查看深圳市自然人税管理系统客户端行业软件Mv3.1.025 官方版

查看中国中医药酒大全行业软件M1.4.20160122 免费绿色版

查看博众时时彩软件(全能版)行业软件Mv2.6.88 官方最新版

查看大管家商业销售管理软件行业软件M

查看华易财务管理软件行业软件Mv5.0.0.0官方版

查看天喜摇号软件行业软件M1.0.0绿色版

查看水泥砼路面计算工具行业软件.02M【免费版】

查看数联云设计模型客户端行业软件Mv3.3.3官方绿色版

查看频率电感电容计算软件行业软件.00M1.0

查看快递100单号查询行业软件.93MV1.5自动识别

查看Arbli查询小工具合集行业软件.52Mv1.0

查看电网技改及检修工程预算软件营改增2016专版行业软件MV3.0免费版

查看三星M332x/382x/402x系列打印机Firmware File更新行业软件MV4.00.01.34官方版

查看比特币挖矿计算器软件行业软件M免费官方版

查看钱宝小助手终结版行业软件Mv2.8 绿色免费版

查看点击查看更多